### PERFORMANCE ENGINEERING OF MULTICORE SOFTWARE: DEVELOPING A SCIENCE OF FAST CODE FOR THE POST-MOORE ERA

by

#### TAO BENJAMIN SCHARDL

#### SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY IN COMPUTER SCIENCE AND ENGINEERING

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 2016

(C) Tao Benjamin Schardl, MMXVI. All rights reserved.

The author hereby grants to MIT permission to reproduce and to distribute publicly paper and electronic copies of this thesis document in whole or in part in any medium now known or hereafter created.

| Author          |            |             |              |          |

|-----------------|------------|-------------|--------------|----------|

| Department of I | Electrical | Engineering | and Computer | Science  |

|                 |            |             | August       | 31, 2016 |

Certified by ..... Charles E. Leiserson Professor of Computer Science and Engineering Thesis Supervisor

Accepted by .....

Professor Leslie A. Kolodziejski Chair, Department Committee on Graduate Theses

#### Performance Engineering of Multicore Software: Developing a Science of Fast Code for the Post-Moore Era

by

Tao Benjamin Schardl

Submitted to the Department of Electrical Engineering and Computer Science on August 31, 2016, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science and Engineering

#### Abstract

The end of Moore's Law, which experts predict to occur in as few as 5 years, means that even average programmers will need to be able to write fast code. Software performance engineering offers great promise to provide computer performance gains in the post-Moore era, but developing efficient software today requires substantial expertise and arcane knowledge of hardware and software systems. Multicore processors are particularly challenging to use efficiently, because doing so requires programmers to engage in parallel programming and to deal with nondeterministic program behavior and parallel scalability concerns.

I contend that we can remedy the *ad hoc* and unprincipled nature of software performance engineering by creating simple and integrated programming technologies for writing fast code. This thesis studies how such technologies can be built by examining nine artifacts that enable principled approaches to tackling nondeterminism and scalability concerns in writing efficient multicore software. Five artifacts develop programming models and theories of performance for writing multicore programs that are efficient both in theory and in practice:

- PBFS, a work-efficient parallel breadth-first search algorithm.

- The Prism chromatic-scheduling algorithm, which executes dynamic data-graph computations deterministically in parallel.

- Ordering heuristics for parallel greedy graph coloring algorithms.

- The pedigree mechanism and DOTMIX algorithm for generating pseudorandom numbers deterministically in parallel in dynamic multithreaded programs.

- The Cilk-P concurrency platform, which provides linguistic and runtime support for deterministic on-the-fly pipeline parallelism.

Three artifacts strive to embed abstract programming and performance models into tools and compilers:

- Cilkprof, a profiler that efficiently measures how each call site in a Cilk program contributes to the program's scalability.

- Rader, a provably good race detector for Cilk programs that use reducer hyperobjects.

- The Tapir compiler intermediate representation, which enables existing compiler optimizations for serial code to optimize across parallel control flow with minimal changes.

The final artifact tackles the complexity of creating efficient diagnostic tools:

• CSI, a framework that provides comprehensive static instrumentation for efficient dynamic-analysis tools.

Together, these artifacts contribute to developing a more coherent science of fast code for multicores than exists today.

Thesis Supervisor: Charles E. Leiserson

Title: Professor of Computer Science and Engineering

#### Acknowledgments

There are numerous people who deserve tremendous thanks for shaping my development as a researcher and as a person, without whom this thesis would not have been possible. I will do my best to thank as many as of them here as I can.

First and foremost, thanks to my advisor, Charles E. Leiserson, for being a phenomenal mentor, teacher, and collaborator. Although I had had some experience doing research before I met Charles, I never knew just how invigorating and fun research can really be until we started working together. His shining example inspires me each day to tackle every problem head-on, to follow every line of inquiry as far as I can, and to strive to be a better writer and teacher.

I would like to thank Saman Amarasinghe and Guy E. Blelloch, for their invaluable feedback and support over the years, as well as their service on my thesis committee. Saman and I have talked many times about the practical side of software performance engineering, including the variety of strange performance anomalies that arise when writing fast code and strategies and techniques for teaching students how to write efficient software. Guy and I have had many discussions on the theoretical side of software performance engineering, and thanks to Guy and his research group, I have had the pleasure of seeing many beautiful parallel algorithms and analysis techniques.

Erik D. Demaine deserves thanks for his advice during my undergraduate career at MIT and for entertaining many research discussions in programming languages, computational geometry, and data structures during my undergraduate career and my early graduate career. Charles, Saman, Guy, and Erik also all deserve many thanks for the indispensable career advice they given me.

Thanks to all of my coauthors who helped me produce the work presented in this thesis.

- Jim Sukha coauthored the DPRNG and Cilk-P papers. I also thank Jim for the many research discussions we have had on pedigrees, random number generators, reducers, pipelining, and Cilk technology.

- I-Ting Angelina Lee coauthored the Cilk-P, Cilkprof, Rader, and CSI papers. Angelina also deserves many thanks for showing me the internals of the Cilk runtime and for research discussions on many topics, including pipelining, reducers, race detection, runtime systems, and compiler instrumentation.

- Zhunping (Justin) Zhang coauthored the Cilk-P paper. I also thank Justin for great discussions on performance-engineering the PARSEC benchmarks using Cilk technology.

- William Hasenplaugh coauthored the Prism and graph-coloring papers. Over my graduate career, Will and I have had many conversations on provably efficient algorithms and proof techniques I had not seen before, for which I am thankful.

- Tim Kaler coauthored the Prism and graph-coloring papers as well. Tim also deserves many thanks for several great conversations on various topics, including efficient data structures, reducers, pedigrees, performance analysis, how to teach software performance engineering, and how to write fast code in the cloud.

- Bradley C. Kuszmaul coauthored the Cilkprof paper and the Life after Moore's Law article. In addition, many thanks to Bradley for collaborating on the textbook and the matrix-multiplication case study, as well as for showing me many esoteric features of programming languages and many brilliant software-performance-engineering tricks.

- William M. Leiserson coauthored the Cilkprof paper. I also thank Will for teaching me about Cilk technology early in my graduate career, for his work in developing the

prototype Cilkprof Pin tool, and for ongoing conversations about parallel programming and programming languages.

- William (Billy) Moses coauthored the Tapir paper, and I commend Billy for his phenomenal efforts in developing the prototype implementation of Tapir in LLVM. Billy also deserves thanks for many discussions on reducers and programming languages.

- Tyler Denniston and Damon Doucet coauthored the CSI paper. I thank both Tyler and Damon for their insights on the design and implementation of CSI. Tyler also deserves thanks for his ongoing efforts in upstreaming CSI into mainstream LLVM.

- Joel S. Emer, Butler W. Lampson, Daniel Sanchez, and Neil C. Thompson all coauthored the Life after Moore's Law article. Thanks to Joel and Daniel for teaching me about modern computer architecture and the impact of Moore's Law. Butler deserves thanks for teaching me about large components and the development of large systems. Many thanks to Neil for teaching me about the economics related to Moore's Law.

In addition to the coauthors and collaborators mentioned so far, I also thank everyone I have collaborated with on different projects and research meetings over the years. Thanks to all of the past and present members of the Supertech research group, especially Kunal Agrawal, Aydın Buluç, Maryam Mehri Dehnavi, Jeremy T. Fineman, Matteo Frigo, Miriam Gershenson, Predrag Gruevski, Shahin Kamali, Matthew Kilgore, Edya Ladan-Moses, Nasro Min-Allah, Eka Palamadai Natarajan, Warut Suksompong, Yuan Tang, James J. Thomas, and Kerry Xing. Thanks to Intel, especially Pablo Halpern, Barry Tannenbaum, and other members of the Cilk team, for discussions on Cilk technology and for incorporating some of our ideas into Intel Cilk Plus. Many thanks to Ronald L. Rivest for his service on my RQE committee and his feedback on the DPRNG paper. Thanks to the participants of various open problem sessions I have attended, especially Zachary Abel, Martin L. Demaine, Sarah Eisenstat, Jayson Lynch, and Isaac Shapiro-Ellowitz. I thank Guy L. Steele Jr. for interesting discussions on fast parallel random-number generation. I thank my collaborators at CMU, including Phillip B. Gibbons, Julian Shun, Harsha Vardhan Simhadri, Kanat Tangwongsan, and the participants of the Parlay research meetings, for showing me many beautiful algorithms. I thank the participants of the parallel video-coding project, especially Daewook Kim, Vivienne Sze, and various visitors from Foxconn. Thanks to Robert C. Miller and Genghis Chau for discussions on visualizing the output of different Cilk tools. I thank our Google sponsors, especially Kostya Serebryany, for their feedback and guidance on the CSI project. Arvind, Christian J. Bell, Adam Chlipala, and Mohsen Lesani deserve thanks for their feedback on Tapir and formal semantics. Thanks to everyone who contributed to discussions on Life after Moore's Law, especially Arvind, Jack Dennis, and Srini Devadas.

Finally, I thank all of my friends and family, especially my sister, Anisa, my brother-inlaw, Matt,<sup>1</sup> and my parents, Chris and Kuey-Chu. Without their inexorable love, support, and encouragement, I never would have made it through my undergraduate and graduate student careers at MIT.

<sup>&</sup>lt;sup>1</sup>Perhaps more commonly known as "Snowflake."

# Contents

| 1        | Intr | roduction                                                        | 11        |

|----------|------|------------------------------------------------------------------|-----------|

|          | 1.1  | Shared-memory-multicore programming                              | 17        |

|          | 1.2  | Developing simple programming models and theories of performance | 21        |

|          | 1.3  | Enhancing the software-development environment                   | 25        |

|          | 1.4  | Thesis statement                                                 | 29        |

|          | 1.5  | Outline                                                          | 29        |

| <b>2</b> | Dyr  | namic Multithreading                                             | <b>31</b> |

|          | 2.1  | Linguistic extensions for fork-join parallelism                  | 31        |

|          | 2.2  | The dag model                                                    | 32        |

|          | 2.3  | Determinacy and races                                            | 33        |

|          | 2.4  | Work-span analysis                                               | 34        |

|          | 2.5  | Scheduling                                                       | 35        |

|          | 2.6  | Parallel reduction mechanisms                                    | 35        |

|          | 2.7  | Worker-local storage                                             | 37        |

| 3        | ΑV   | Vork-Efficient Parallel Breadth-First Search Algorithm           | 39        |

|          | 3.1  | Introduction                                                     | 39        |

|          | 3.2  | The PBFS algorithm                                               |           |

|          | 3.3  | The bag data structure                                           |           |

|          | 3.4  | Experimental results                                             |           |

|          | 3.5  | Modeling reducers                                                |           |

|          | 3.6  | Analysis of programs with nonconstant-time reducers              |           |

|          | 3.7  | Analyzing PBFS                                                   |           |

|          | 3.8  | Conclusion                                                       |           |

|          |      |                                                                  |           |

| 4        |      | cuting Dynamic Data-Graph Computations Deterministically Using   |           |

|          |      | comatic Scheduling                                               | 63        |

|          | 4.1  | Introduction                                                     | 63        |

|          | 4.2  | The PRISM algorithm                                              |           |

|          | 4.3  | The multibag data structure                                      |           |

|          | 4.4  | Analysis of Prism                                                | 74        |

|          | 4.5  | Empirical evaluation                                             | 75        |

|          | 4.6  | The PRISM-R algorithm                                            | 80        |

|          | 4.7  | The multivector data structure                                   | 82        |

|          | 4.8  | Analysis and evaluation of PRISM-R                               | 86        |

|          | 4.9  | Conclusion                                                       | 87        |

| <b>5</b> | Ord  | ering Heuristics for Parallel Graph (      | Col | ori | ng   |     |     |       |     |     |   |   | 89  |

|----------|------|--------------------------------------------|-----|-----|------|-----|-----|-------|-----|-----|---|---|-----|

|          | 5.1  | Introduction                               |     |     |      |     |     |       |     |     |   |   | 89  |

|          | 5.2  | The Jones-Plassmann algorithm              |     |     |      |     |     |       |     |     |   |   | 94  |

|          | 5.3  | JP with random ordering                    |     |     |      |     |     |       |     |     |   |   | 95  |

|          | 5.4  | The LF and SL heuristics                   |     |     |      |     |     |       |     |     |   |   |     |

|          | 5.5  | Log ordering heuristics                    |     |     |      |     |     |       |     |     |   |   |     |

|          | 5.6  | Empirical evaluation                       |     |     |      |     |     |       |     |     |   |   |     |

|          | 5.7  | Implementation techniques                  |     |     |      |     |     |       |     |     |   |   |     |

|          | 5.8  | Evaluation of serial ordering heuristics . |     |     |      |     |     |       |     |     |   |   |     |

|          | 5.9  | Related work                               |     |     |      |     |     |       |     |     |   |   |     |

|          | 0.0  | Conclusion                                 |     |     |      |     |     |       |     |     |   |   |     |

|          |      | Recent developments                        |     |     |      |     |     |       |     |     |   |   |     |

|          | 0.11 | fielent developments                       | • • | •   |      | •   | ••• | <br>• | ••• | • • | • | • | 110 |

| 6        | Det  | erministic Parallel Random-Number          | Ge  | ene | rati | ion |     |       |     |     |   |   | 115 |

|          | 6.1  | Introduction                               |     |     |      |     |     |       |     |     |   |   | 115 |

|          | 6.2  | Pedigrees                                  |     |     |      |     |     |       |     |     |   |   |     |

|          | 6.3  | DOTMIX: A pedigree-based DPRNG             |     |     |      |     |     |       |     |     |   |   |     |

|          | 6.4  | Other pedigree-based DPRNG's               |     |     |      |     |     |       |     |     |   |   |     |

|          | 6.5  | A scoped DPRNG library interface           |     |     |      |     |     |       |     |     |   |   |     |

|          | 6.6  | Performance results                        |     |     |      |     |     |       |     |     |   |   |     |

|          | 6.7  | Related work                               |     |     |      |     |     |       |     |     |   |   |     |

|          | 6.8  | Concluding remarks                         |     |     |      |     |     |       |     |     |   |   |     |

|          | 6.9  | Recent developments                        |     |     |      |     |     |       |     |     |   |   |     |

|          | 0.0  |                                            | • • | •   |      | ·   | ••• | <br>• | ••• | • • | · | • | 101 |

| 7        | On-  | the-Fly Pipeline Parallelism               |     |     |      |     |     |       |     |     |   |   | 139 |

|          | 7.1  | Introduction                               |     |     |      |     |     |       |     |     |   |   | 139 |

|          | 7.2  | On-the-fly pipeline programs               |     |     |      |     |     |       |     |     |   |   | 143 |

|          | 7.3  | On-the-fly pipelining of $x264$            |     |     |      |     |     |       |     |     |   |   |     |

|          | 7.4  | Computation-dag model                      |     |     |      |     |     |       |     |     |   |   |     |

|          | 7.5  | The PIPER scheduler                        |     |     |      |     |     |       |     |     |   |   |     |

|          | 7.6  | Structural invariants                      |     |     |      |     |     |       |     |     |   |   |     |

|          | 7.7  | Time analysis of PIPER                     |     |     |      |     |     |       |     |     |   |   |     |

|          | 7.8  | Space analysis of PIPER                    |     |     |      |     |     |       |     |     |   |   |     |

|          | 7.9  | Cilk-P runtime design                      |     |     |      |     |     |       |     |     |   |   |     |

|          |      | Evaluation                                 |     |     |      |     |     |       |     |     |   |   |     |

|          |      | Pipeline throttling                        |     |     |      |     |     |       |     |     |   |   |     |

|          |      | Conclusion                                 |     |     |      |     |     |       |     |     |   |   |     |

|          |      | Recent developments                        |     |     |      |     |     |       |     |     |   |   |     |

|          | 1.10 |                                            | • • | •   |      | •   | ••• | <br>• | ••• | • • | • | • | 100 |

| 8        | The  | Cilkprof Scalability Profiler              |     |     |      |     |     |       |     |     |   |   | 181 |

|          | 8.1  | Introduction                               |     |     |      |     |     |       |     |     |   |   | 181 |

|          | 8.2  | Parallel quicksort                         |     |     |      |     |     |       |     |     |   |   |     |

|          | 8.3  | Computing work and span                    |     |     |      |     |     |       |     |     |   |   |     |

|          | 8.4  | The basic profile algorithm                |     |     |      |     |     |       |     |     |   |   |     |

|          | 8.5  | The prof data structure                    |     |     |      |     |     |       |     |     |   |   |     |

|          | 8.6  | The profile                                |     |     |      |     |     |       |     |     |   |   |     |

|          | 8.7  | Empirical evaluation                       |     |     |      |     |     |       |     |     |   |   |     |

|          | 8.8  | Case study: PBFS                           |     |     |      |     |     |       |     |     |   |   |     |

|    | 8.9  | Related work                                                    | . 202      |

|----|------|-----------------------------------------------------------------|------------|

|    | 8.10 | Conclusion                                                      |            |

|    |      |                                                                 |            |

| 9  | Rac  | e Detection for Cilk Programs That Use Reducer Hyperobjects     | 205        |

|    | 9.1  | Introduction                                                    |            |

|    | 9.2  | Examples of races that involve a reducer                        |            |

|    | 9.3  | The PEER-SET algorithm                                          |            |

|    | 9.4  | Correctness of the Peer-Set algorithm                           | . 213      |

|    | 9.5  | The SP+ algorithm                                               |            |

|    | 9.6  | The spawn parse tree and the view parse tree                    | . 223      |

|    | 9.7  | Correctness of the SP+ algorithm                                | . 230      |

|    | 9.8  | Analysis of the SP+ algorithm                                   | . 233      |

|    | 9.9  | Rader                                                           | . 235      |

|    | 9.10 | Related work                                                    | . 239      |

|    | 9.11 | Conclusion                                                      | . 240      |

|    | 9.12 | Recent developments                                             | . 241      |

|    |      |                                                                 |            |

| 10 | Tap  | ir: Embedding Fork-Join Parallelism into LLVM's Intermediate Re | p-         |

|    |      | entation                                                        | <b>243</b> |

|    |      | Introduction                                                    |            |

|    |      | Tapir                                                           |            |

|    | 10.3 | Analysis passes                                                 | . 253      |

|    | 10.4 | Denotational semantics for Tapir                                | . 255      |

|    | 10.5 | Optimization passes                                             | . 263      |

|    | 10.6 | Auxiliary software                                              | . 266      |

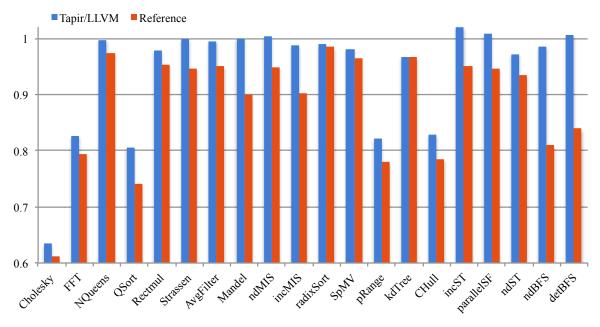

|    | 10.7 | Evaluation                                                      | . 266      |

|    | 10.8 | Related work                                                    | . 270      |

|    | 10.9 | Conclusion                                                      | . 272      |

|    |      |                                                                 |            |

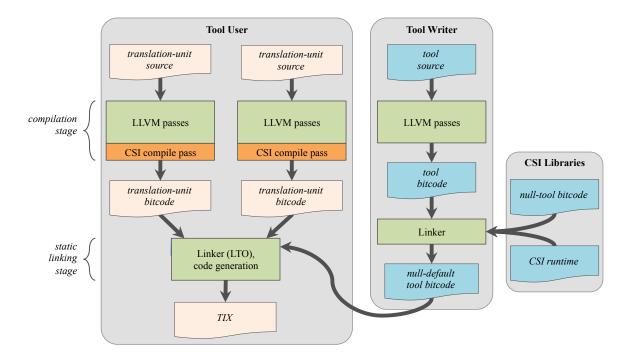

| 11 |      | nprehensive Static Instrumentation for Dynamic-Analysis Tools   | 273        |

|    |      | Introduction                                                    |            |

|    |      | The CSI instrumentation API                                     |            |

|    | 11.3 | An example CSI-tool                                             | . 284      |

|    | 11.4 | Implementation                                                  | . 286      |

|    | 11.5 | Demonstration CSI-tools                                         | . 290      |

|    | 11.6 | Related work                                                    | . 297      |

|    | 11.7 | Conclusion                                                      | . 297      |

| 12 | Life | after Moore's Law                                               | 299        |

## Chapter 1

# Introduction

With a growing number of indications that the end of Moore's Law is imminent — meaning that advances in silicon fabrication technology can no longer sustain the historical exponential growth of computer performance — even average programmers will soon need to be able to write efficient software. Although programmers can find considerable gains in computer performance through "software performance engineering," writing efficient software today requires substantial expertise and arcane knowledge. I contend that the process of writing efficient software can be made accessible to average programmers by building simple and integrated software-performance-engineering technologies. In particular, building these technologies serves to develop a more coherent science of fast code than exists today. This thesis examines the development of such technologies by examining nine artifacts that support principled approaches to tackling complex issues in writing fast multicore programs.

Software performance — how quickly code runs and how efficiently it uses computing resources, such as memory, energy, network bandwidth, secondary storage, etc. — dictates the cost of running an application on a computing device. Every software application requires some time and computing resources in order to run, and new software functionality requires additional computing resources to run alongside existing applications. Optimizing a program for performance ensures that computing devices can meet the resource requirements of that program. Recently, cloud computing [14, 15, 23, 138, 166] has generated monetary incentives for optimizing software performance. The monetary cost of running an application in the cloud scales with its running time [16]. Minimizing the running time of the application therefore minimizes the cost of running that application in the cloud.

Despite the monetary and human costs of slow code, *software performance engineering* — the rewriting code to run faster and use computing resources more efficiently is a notoriously difficult task [221]. Attempting to improve a program's performance tends to complicate its codebase, making the code difficult to understand, maintain, and debug. Furthermore, programmers often demonstrate a poor intuitive understanding of where programs spend their execution time. As a result, programmers can waste significant time and energy making code more complicated without actually improving its performance. These issues with software performance engineering have been known since the 1970's and 1980's, when several famous criticisms were made of programmers attempting to improve software performance:

Premature optimization is the root of all evil.

—Donald Knuth, 1979 [221]

| Version | Implementation              | $\begin{array}{c} Running\\ time \ (s) \end{array}$ | GFLOPS  | Absolute<br>speedup | $\begin{array}{c} Relative\\ speedup \end{array}$ | Fraction<br>of peak |

|---------|-----------------------------|-----------------------------------------------------|---------|---------------------|---------------------------------------------------|---------------------|

| 1       | Python                      | $25,\!552.48$                                       | 0.005   | 1                   |                                                   | 0.00%               |

| 2       | Java                        | $2,\!372.68$                                        | 0.058   | 11                  | 10.8                                              | 0.01%               |

| 3       | $\mathbf{C}$                | 542.67                                              | 0.253   | 47                  | 4.4                                               | 0.03%               |

| 4       | Parallel loops              | 69.80                                               | 1.969   | 366                 | 7.8                                               | 0.24%               |

| 5       | Parallel divide-and-conquer | 3.80                                                | 36.180  | 6,727               | 18.4                                              | 4.33%               |

| 6       | + vectorization             | 1.10                                                | 124.914 | 23,224              | 3.5                                               | 14.96%              |

| 7       | + AVX intrinsics            | 0.41                                                | 337.812 | $62,\!806$          | 2.7                                               | 40.45%              |

| 8       | Strassen                    | 0.38                                                | 361.177 | $67,\!150$          | 1.1                                               | 43.24%              |

Figure 1-1: Performance gains from iteratively performance-engineering a program on a modern multicore machine to multiply two  $4096 \times 4096$  matrices of double-precision floating-point numbers. "Time" is the running time in seconds of the particular code. "GFLOPS" is the giga-FLOPS billions of floating-point operations per second — that the code achieved. "Absolute speedup" is the ratio of the running time of the code to that of the Python code in Version 1 of the table. "Relative speedup" is the ratio of the running time of the code to the running time of the code on the preceding line of the table. "Fraction of peak" is the percentage of the computer's maximum double-precision floating-point capability, which is 835 GFLOPS. The "GFLOPS" and "Percent of peak" values for Strassen are computed based on time, as if Strassen actually performed  $2 \cdot 4096^3$  floating-point operations in its running time. Each running time is the minimum of 5 runs on an Amazon AWS c4.8xlarge spot instance, which is a dual-socket Intel Xeon E5-2666 v3 system with a total of 60 GiB of memory. Each Xeon is a 2.9 GHz 18-core CPU with a shared 25 MiB L3-cache. Each processor core has a 32 KiB private L1-data-cache and a 256 KiB private L2-cache. The machine was running Fedora 22, using version 4.0.4 of the Linux kernel. The Python version was executed using Python 2.7.9. The Java version was compiled and run using OpenJDK version 1.8.0 51. All other versions were compiled using GCC  $5.2.1\ 20150826$ .

More computing sins are committed in the name of efficiency (without necessarily achieving it) than for any other single reason — including blind stupidity. —*William Wulf, 1979 [410]*

The First Rule of Program Optimization: Don't do it. The Second Rule of Program Optimization — For experts only: Don't do it yet. —*Michael A. Jackson (quoted by Jon Bentley, 1988 [39])*

These criticism were originally uttered in response to programmers using **goto** statements in complicated ways in efforts to improve software efficiency. These efforts would produce codes that are difficult to reason about and debug. Although programmers today typically use structured control flow, such as conditionals and loops, instead of **goto** statements, the act of writing fast code still tends to produce complicated code that is difficult to understand, maintain, and debug.

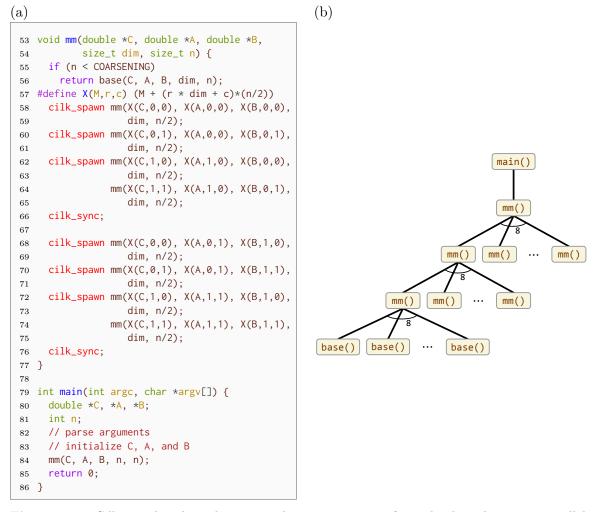

To illustrate the complexity and payoff of software performance engineering today, consider a simple example: matrix multiplication. Figure 1-1 presents the results of a case study my colleagues<sup>1</sup> and I undertook to performance-engineer a program that multiplies two  $4096 \times 4096$  matrices on a shared-memory multicore machine.<sup>2</sup> Version 1 reflects what a programmer today might initially implement to solve the problem: multiply the two matrices using three nested loops in Python, one of today's most popular high-level programming languages. As the table shows, this code takes 7 hours to run and achieves less than 1/150,000 of the machine's peak performance.

<sup>&</sup>lt;sup>1</sup>I collaborated with Bradley C. Kuszmaul and Charles E. Leiserson on this case study.

<sup>&</sup>lt;sup>2</sup>This case study was originally inspired by Saman Amarasinghe.

Starting from the Python implementation, we engineered this software for performance using a variety of techniques. Simply choosing a more efficient programming language speeds up this calculation dramatically. For example, coding it in Java (Version 2) produces a speedup of  $10.8 \times$ , and coding it in C (Version 3) produces an additional speedup of  $4.4 \times$ , or 47 times faster than the original Python code. "Form-fitting" the matrix code to take advantage of the hardware makes it still faster. By parallelizing the code to run on all 16 of the processor cores (Version 4), exploiting the cache hierarchy (Version 5), vectorizing the code (Version 6), and exploiting Intel's special AVX chip instructions (Version 7), the matrix-multiplication task can be solved in 0.41 seconds. By using Strassen's celebrated algorithm [375] for matrix multiplication, the highly optimized matrix-multiplication code in Version 7 of Figure 1-1 can be improved about 10% to achieve a running time of 0.38 seconds, a 67,000 × speedup over the original Python code.

This case study also illustrates the difficulty of writing fast code. Today, there are three general techniques to improve software efficiency, each of which complicates programming. (1) Adopt low-level programming languages and avoid high-level programming technologies that trade off performance for ease of programming. (2) Refactor code to exploit architectural features, including parallelism, cache hierarchy, and vectorization. (3) Rewrite code to use more efficient algorithms. When all of these techniques are applied in the case study, the resulting efficient parallel Strassen implementation (Version 8) is over 850 lines of code, which is 40 times the number of lines in the original Python implementation (Version 1). It took us over 100 hours of programmer effort to produce the Strassen code, even though we availed ourselves of the latest software-performance-engineering technology produced by recent research. Of course, for the specific problem of matrix multiplication, one can simply call an already optimized routine, such as DGEMM from the Intel Math Kernel Library (MKL) [200], which is almost as fast as Version 8. For arbitrary pieces of code where such libraries are not available, however, programmers must use these techniques themselves and deal with the concomitant programming difficulties. As the study shows, there exists a vast distance in both program efficiency and programming difficulty between simple code and fast code.

#### Software performance engineering and Moore's Law

Should average programmers worry about writing fast code? Programmers today often don't concern themselves with engineering software for performance, in part because of "Moore's Law." In 1965 Intel founder Gordon Moore observed the steady trend of transistor miniaturization [287], and in 1975 he predicted that the number of transistors per computer chip would double every two years [288]. This trend was christened **Moore's Law** by Caltech professor Carver Mead (although the precise origins are actually a bit murky [102]) and has held since 1975. Until about 2006, smaller transistors were also faster and more energy efficient [109], which enhanced the speed and capacity of computers. Moore's Law is responsible for cellphones today that are more powerful than the room-sized computers from just 25 years ago, for providing nearly half the world's people with access to all the world's information on the Internet [202], and for drug discoveries enabled by powerful supercomputers. With Moore's Law providing programmers with "free" computer performance, programmers found little economic incentive to struggle with the complex task of writing fast code and instead focused on minimizing the development time of their applications.

Because of both fundamental physical limits and because of the economics of chip manufacturing, however, it appears that Moore's Law will end soon. Technology leaders, such as Robert Colwell [95] and the International Technology Roadmap for Semiconductors [203] have predicted the demise of Moore's Law to occur as early as 2020. Even Intel, the leader in semiconductor-device technology, has acknowledged a significant attenuation in the rate of shrinking device sizes [201, p. 14].

After the demise of Moore's Law, programmers must find other opportunities for computer performance to grow. The case study in Figure 1-1 suggests that programmers can find substantial performance gains by performance-engineering software. For example, consider a simple conception of Moore's Law that says that computers get twice as powerful every two years.<sup>3</sup> Then the speedup factor of 67,000 achieved by the Strassen implementation (Version 8) over the original Python program (Version 1) amounts to over 32 years of Moore's Law improvements. Other promising results can be found in studies in performance-engineering large graph-processing codes [320] and in performance-engineering the "connectomics" pipeline for processing images of brain tissue to determine neural connectivity [253, 353]. Although these problems are often thought to require large clusters of machines to solve, these studies successfully performance-engineering software for today's machines still requires substantial expertise and arcane knowledge, as the case study in Figure 1-1 illustrates. How can we expect average programmers to do such optimizations?

#### Previous research on software performance engineering

Decades of research effort have gone into mitigating the complexity of software performance engineering. This research effort has produced an array of technologies that support principled approaches to writing and reasoning about fast code, including programming languages and frameworks, compilers, performance analysis tools, theoretical models of performance, provably efficient algorithms, and methodologies for developing efficient software.

Several fundamental tools and methodologies for writing efficient software find their origins in the 1970's and 1980's. In 1971, Knuth developed the first program **profiler** to measure how frequently a program executed each of its statements [220]. Knuth and other programmers used the resulting program profiles to identify bottlenecks in the execution time of a program and to direct their optimization efforts towards those bottlenecks. In 1975, Wulf *et al.* developed one of the earliest optimizing compilers [411], which empowered programmers to use higher-level programming-language constructs without sacrificing undue performance. In 1982, Bentley authored a short treatise on software performance engineering, entitled Writing Efficient Programs [38], which presents a set of simple rules for programmers to apply to their source code to optimize their program's performance. Although some of these rules have been encoded into optimizing compilers or have grown obsolete with advances in computer hardware, many of these rules are still applicable today.

Thanks to ongoing research and development efforts, programmers today can avail themselves of an abundance of diagnostic tools, compilers, and programming models to simplify the task of performance-engineering software for modern machines. A host of dynamic-analysis tools, such as race detectors [123, 124, 134, 280, 281, 343, 351], memory checkers [31,177,350], cache simulators [121,377,407], call-graph generators [171,205], codecoverage analyzers [390,397], and performance profilers [171,329,401], have been built that allow programmers to study how an executing program spends its time and computing

$<sup>^{3}</sup>$ In fact, computer performance has grown at slower and faster rates over time [181], but this thesis uses this commonly accepted definition for simplicity.

resources. Modern multicore processors contain hardware performance counters that diagnostic tools can employ to gain detailed insight into how a program utilizes the hardware. Mainstream compilers, including GCC [369], ICC [198], and LLVM [232], are all optimizing compilers that are designed to handle multiple front-end programming languages and multiple back-end machine architectures. "Just-in-time" compilers have been created that compile and optimize a program as it executes (see [25] for a history). These compiler technologies allow a wide variety of software to enjoy the benefits of compilation and automatic optimization. Tools such as autotuners [18, 19, 91, 142, 322, 400, 404] and polyhedral optimization frameworks [63,172] have been built to perform elaborate optimizations on specific types of programs or program structures. Parallel building blocks [357] and "dynamic multithreading concurrency platforms" (described in Section 1.1) have been built that temper the complexity parallel programming. Domain-specific languages have emerged that simplify the task of writing efficient programs in specific problem domains. The Halide programming language [323] aims to enable performance engineers to quickly iterate through a variety of image-processing-pipeline implementations to zero in on the fastest one. The Julia programming language [44] simplifies the task of writing fast programs in technical computing. Several frameworks have been created to support efficient computations on graphs, including GraphLab [264, 265] Pregel [269], Galois [298, 299], PowerGraph [165], Ligra [358, 361], and GraphChi [228].

Immense research effort has also gone into creating efficient algorithms and data structures for numerous problems, as well as creating analytical techniques and performance models for justifying an algorithm's efficiency [9, 101, 223, 349]. Although most algorithms and data structures are designed to optimize the serial running time of a computation, theoretical performance models have been developed to address particular features of modern multicore hardware. We now have many good performance models for parallel machines, including the parallel random-access machine (PRAM) model and its variants (see [214] for a survey), the bulk-synchronous model [393], the work-span model [100, Ch. 27], the logP model [105], fixed-connection networks [244, Sec. 1.1], and even Boolean circuits [396]. Meanwhile, performance models, such as external memory model and its variants [5, 145] and the parallel external memory model [21] allow programmers to analyze performance in terms of memory accesses, which are relatively expensive operations on modern machines. Theoretical performance models have also emerged to account for high-latency operations such as file I/O in parallel programs [291].

Given these numerous developments, why does software performance engineering continue to be an art that requires considerable expertise and arcane knowledge to carry out? From my own research experience, I find that many existing performance-engineering technologies are difficult to use because they are not *integrated*. For example, many theoretically efficient algorithms and data structures described in the literature have never been implemented, leaving the question of whether their theoretical efficiency can be borne out in practice unresolved. Furthermore, most algorithms are still designed to minimize only their asymptotic serial running time, and relatively little attention is paid to "form-fitting" these algorithms to efficiently utilize modern multicore hardware. Meanwhile, existing diagnostic tools and compilers are often difficult to use because their behavior does not reflect the simple programming and performance models used to write efficient software. Diagnostic tools can produce results that defy interpretation in terms of the models, while compilers can fail to perform optimizations that are simple and straightforward in light of the programming model. Although some developments, such as the dynamic multithreading concurrency platforms described in Section 1.1, combine sets of performance-engineering

| Artifact | Simple programming models | Theories<br>of performance | $Diagnostic \ tools$ | Compilers |

|----------|---------------------------|----------------------------|----------------------|-----------|

| PBFS     | •                         |                            |                      |           |

| Prism    |                           |                            |                      |           |

| Color    | •                         | •                          |                      |           |

| DPRNG    | •                         |                            |                      |           |

| Cilk-P   | •                         | •                          |                      |           |

| Cilkprof | •                         | •                          | •                    |           |

| Rader    | •                         |                            | •                    |           |

| Tapir    | •                         |                            |                      | •         |

| CSI      | •                         |                            | •                    |           |

Figure 1-2: Illustration of the high-level software-performance-engineering technologies used or developed by each artifact presented in this thesis. The first column lists the artifacts in this thesis, while the remaining columns identify high-level software-performance-engineering technologies: column two denotes simple programming models, column three denotes theories of performance, column four denotes diagnostic tools, and column five denotes compilers. Each row corresponds to a thesis artifact. A circle indicates that a particular thesis artifact used or developed a particular technology. "PBFS" identifies my work on a work-efficient parallel breadth-first search algorithm (Chapter 3). "Prism" identifies my work on the Prism chromatic-scheduling algorithm for dynamic data-graph computations (Chapter 4). "Color" identifies my work on ordering-heuristics for parallel graph coloring (Chapter 5). "DPRNG" identifies my work on deterministic parallel random-number generation (Chapter 6). "Cilk-P" identifies my work on the Cilk-P concurrency platform for on-thefly pipeline parallelism (Chapter 7). "Cilkprof" identifies my work on the Cilkprof scalability profiler (Chapter 8). "Rader" identifies my work on the Rader race detector for Cilk programs that use reducer hyperobjects (Chapter 9). "Tapir" identifies my work on the Tapir compiler intermediate representation for dynamic multithreaded programs (Chapter 10). "CSI" identifies my work on the CSI compiler instrumentation framework (Chapter 11).

technologies, further integration of these technologies is needed to reduce the expertise and arcane knowledge required to write fast code.

#### Contributions

I contend that we can remedy the *ad hoc* and unprincipled nature of software performance engineering by transforming the writing of fast code into a more coherent engineering science. To do so, the disparate technologies that support software performance engineering must be integrated and new technologies must be developed. Programming models, theories of performance, compilers, and tools must all work together to reduce the complexity of writing fast code and reasoning about its behavior and efficiency. As long as programmers must reconcile the diverse assumptions and behaviors of different performance-engineering technologies themselves, writing fast code will continue to be more of an art than a science. Only by integrating the various aspects of software development can performance engineers hope to realize the central promise of science: the ability to make testable predictions about how things behave. Today, programmers generally must choose between writing simple code they can understand or writing fast code. I contend that we can reduce the distance between simple code and fast code by building integrated software-performance-engineering technologies and developing a more coherent science of efficient software.

This thesis explores how simple and integrated software-performance-engineering technologies can be built by studying nine artifacts that tackle complex issues facing performance engineers when writing efficient multicore software. Figure 1-2 illustrates the set of high-level software-performance-engineering technologies that are used or developed by each thesis artifact. As the figure shows, the first five artifacts develop simple programming models and theories of performance that enable principled approaches to reasoning about the behavior and efficiency of multicore software. The remaining four artifacts focus on the diagnostic tools and compilers in the software-development environment. Three of these artifacts work to embed the abstract programming models and theories of performance for efficient multicore software into these diagnostic tools and compilers. This embedding strives to ensure that the behavior of the development environment conforms to the programmer's reasoning about the program's performance and behavior. The final artifact introduces a simple programming model for creating new efficient diagnostic tools. Together, these artifacts examine how software-performance-engineering technologies can be built and integrated to support principled, scientific approaches to reasoning about the behavior and performance of fast code for multicores.

The remainder of this chapter overviews the challenges in writing fast multicore software and how the nine artifacts presented in this thesis develop technologies to support principled, scientific approaches to addressing these challenges. Section 1.1 describes "shared-memory multicore machines" and the major issues of "nondeterminism" and "scalability" that complicate multicore-software performance engineering. This section also describes prior work on "dynamic multithreading" to address some of these issues. Section 1.2 describes the first five artifacts and how they develop simple programming models that admit theories of performance for writing and reasoning about efficient multicore software. Section 1.3 describes the last four artifacts, which look to enhance the software-development environment to support principled approaches to reasoning about the behavior and performance of multicore programs. Section 1.4 reviews the statement of this thesis, and Section 1.5 outlines the remaining chapters of this thesis.

#### 1.1 Shared-memory-multicore programming

Most of the artifacts presented in this thesis tackle the complexity of writing efficient software for a *shared-memory multicore machine* (or simply a *multicore*), which is a computer that contains multiple general-purpose processor cores that share a common main memory. This section describes why studying shared-memory multicores will be important in the post-Moore era. This section also describes parallel programming, one of the largest and most difficult problems in programming multicores, and the main concerns of "nondeterminism" and "scalability" that make writing fast multicore programs particularly challenging. I briefly outline "dynamic multithreading" technology,<sup>4</sup> which makes substantial progress in addressing nondeterminism and scalability issues in multicore programming. Chapter 2 describes dynamic multithreading in greater detail.

One reason for why multicore programming will be important in the post-Moore era comes from their ubiquity in the computing environment. Multicores entered the marketplace around the mid-2000's, when processor manufacturers could no longer run transistors at higher frequencies due to physical limitations on processor hardware, specifically, on the power density of silicon technology. Since then, multicore processors have proliferated to

<sup>&</sup>lt;sup>4</sup>Also called  $task \ parallelism$ .

become the "bargain" processor component that is widely employed in building a variety of computing devices, large and small. Mobile computing systems such as tablets and smartphones are typically built using a multicore processor chip. Large, complex systems, meanwhile, such as datacenters for cloud computing, grid computers, high-performance clusters, and supercomputers, are often built from collections of shared-memory multicore machines.

Shared-memory multicore machines are also simpler to program than distributed systems. Although a cluster of multicore machines has greater total capacity than any single multicore, coordinating parallel tasks in a distributed computing environment often involves moving data between machines, which incurs high performance costs. As a result, machines in distributed environments often exhibit poor utilization — software achieves little of the total potential computer performance of the cluster. In a multicore, however, main memory is shared between processor cores. As a result, data need not be copied to coordinate parallel operations, and the cost of this coordination is thereby significantly reduced. Software thus has an easier time achieving high machine utilization on a single multicore.

Furthermore, individual multicores have grown to be quite large and powerful. A single multicore system today is able to fit a whole database system within its memory [78]. A host of other applications across domains such as computational science, real-world modeling, machine learning, and image and video processing, are designed to run on multicore computers, because multicores represent a "sweet spot" in cost for performance. The aforementioned studies in large graph-processing problems and the "connectomics" image-processing pipeline demonstrate the capacity of multicores to solve problems that are typically thought to be too large for a single machine. Shun argues persuasively that single shared-memory machines are sufficient for solving many problems in large-scale computing [357].

Software often fails to realize the computer performance available within a single multicore, however. John Hennessy<sup>5</sup> acknowledged this trend when he said,

We switched to multicore, but we have not made it as useful as if we had just made single-threaded processors faster.

—John Hennessy [312]

The matrix-multiplication case study presented in Figure 1-1 reflects this trend as well. As the figure shows, software-performance-engineering effort beyond simply programming in a more efficient language is required to make the program utilize more than 1% of the machine's peak performance.

One reason why software tends to underutilize multicores is because multicores are complicated. A multicore contains a host of interconnected computing resources, including one or more processor chips, each of which contains multiple processor cores. Typically, a processor core is a pipelined, superscalar processing unit that includes multiple functional units, vector units, out-of-order execution, branch predictors, hardware prefetchers, hyperthreads, and one or more levels of local cache. Each processor also shares a last-level cache among all of its cores, while the machine itself contains a main memory that is shared by all of its processors. Different shared-memory multicores might contain additional computing resources, such as a network, a graphics-processing unit (GPU), a disc, or a battery. Utilizing all of these hardware features of a shared-memory multicore machine is a complex task that requires significant expertise and arcane knowledge.

<sup>&</sup>lt;sup>5</sup>President of Stanford University, parallel-computing pioneer, and coauthor of *Computer Architecture:* A Quantitative Approach.

#### Parallel programming

Using parallel processor cores efficiently involves parallel programming, which poses one of the largest and most difficult problems in programming multicores. Parallel programming is also involved in using other multicore hardware, such as GPU's and vector units. Although ongoing important research efforts seek ways to apply these hardware systems for general computation, most software today employs these systems in an *ad hoc* and opportunistic fashion. This thesis instead focuses on programming the general-purpose processor cores, which are responsible for executing the vast majority of software running on multicores today.

To illustrate some of the challenges involved in parallel programming, let us consider writing a parallel program using Pthreads [188], a standard API for threading that is used to write many parallel programs today. The Pthreads API provides a set of library functions for creating and managing parallel operating-system threads. To write a program using Pthreads, the programmer explicitly creates each parallel thread, or Pthread, and assigns it computation to execute. The operating-system scheduler then takes care of executing these Pthreads asynchronously on processor cores. Pthreads communicate with each other and exchange data through shared memory, and programmers can coordinate updates to shared variables by employing mechanisms such as mutex locks or condition variables.

The Pthreading model forces programmers to deal with several difficult problems in reasoning about the behavior and performance of a parallel program. Pthreaded programs can behave *nondeterministically*, based on how the operating system chooses to schedule and execute different Pthreads in any particular run of the program. Reasoning about the behavior of a Pthreaded program therefore involves considering all of the exponentially many possible timings (interleavings) of the computations running on different Pthreads, which is difficult and error-prone. Furthermore, nondeterministic behavior confounds traditional debugging strategies, because a programmer cannot reliably expose buggy behavior over and over to zero in on a bug. Meanwhile, the programmer must account for several factors to optimize the performance of a Pthreaded program. Because creating a Pthread is an expensive operation, taking longer than 10,000 cycles, the programmer must amortize this overhead over a reasonably large amount of computation allocated to each Pthread. A typical strategy for minimizing this overhead is to create only as many Pthreads as there are processors on the system. Programmers must then strive to avoid serial bottlenecks and to balance the computation among these Pthreads. These complications are amplified when scalability is considered, that is, how quickly the program runs on different machines with different numbers of processor cores. Problems of nondeterminism and scalability are not unique to Pthreads, but persist in other threading models as well.

The nondeterminism of multithreaded programs has been viewed as a key reason that programming large-scale parallel applications remains error prone and difficult [235]. In response to the problem of nondeterminism, many researchers over multiple decades have advocated that the difficulty of parallel programming can be greatly reduced by using some form of deterministic parallelism [41, 42, 51, 60, 113, 114, 134, 158, 174, 187, 304, 310, 370, 414]. With a deterministic parallel program, the programmer observes no logical *concurrency*, that is, no nondeterminacy in the behavior of the program due to the relative timing of communicating processes such as occurs when one process arrives at a lock before another.<sup>6</sup>

<sup>&</sup>lt;sup>6</sup>Netzer and Miller [297] distinguish *internal* determinacy, where the program contains no determinacy races, from *external* determinacy, where the final answer of the program is the same from run to run. The work presented in this thesis generally seeks to avoid *programmer-observable* nondeterministic behavior.

The semantics of a deterministic parallel program therefore match those of a corresponding serial program, and reasoning about such a program's correctness, at least in theory, is no harder than reasoning about the correctness of a serial program. Testing, debugging, and formal verification are simplified, because there is no need to consider all possible relative interleavings of operations on shared mutable state. Furthermore, Blelloch *et al.* [52] argue persuasively that price of determinism in performance need not be high, and in particular, that deterministic parallel algorithms can be fast.

Despite the apparent advantages of deterministic parallelism, however, many parallel codes deployed in practice still exhibit nondeterministic behavior. For example, all the codes in the PARSEC [45], Galois [315], and STAMP [79] benchmark suites use concurrency mechanisms, such as mutex locks and condition variables, which behave nondeterministically. Part of the reason that many parallel programs are still nondeterministic is that existing parallel-programming environments are immature and do not provide good support for deterministic parallel programming. Indeed, concurrency mechanisms are the building blocks for synchronization in most parallel-programming environments. Programmers are familiar with locks and condition variables, and even generalizing them to transactional memory [182] does not mitigate their inherent nondeterminacy. Some approaches to determinism — such as data parallelism [224], commutative operations [331, 370], and various effect systems [60] — do not seem general enough to handle more than a limited set of real-life applications. Purely functional programming is perhaps the most straightforward way to achieve deterministic parallelism, because functional programming precludes parallel threads from interacting [51,174], but few real-world codebases employ functional languages. Because of the prevalence of nondeterminism, only experts can program these parallel applications, especially those for shared-memory platforms, and these bug-prone codes can only be understood by experts.

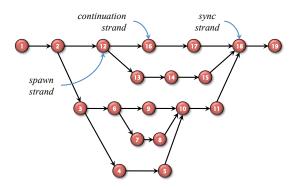

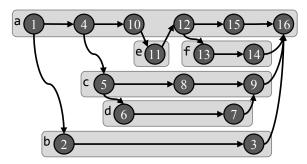

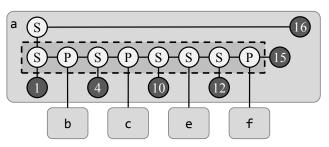

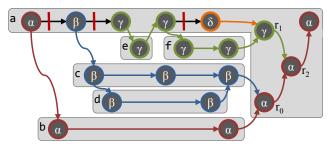

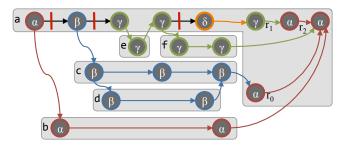

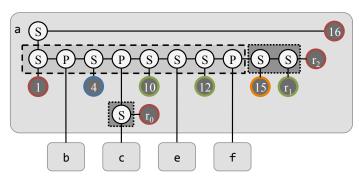

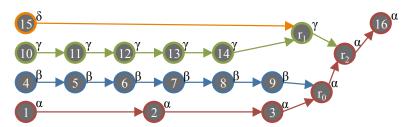

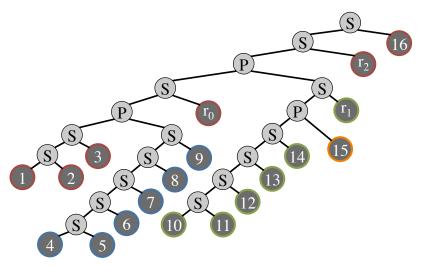

#### Dynamic multithreading

Tremendous progress has been made in mitigating the problems posed by nondeterminism and scalability in parallel programming. Concurrency platforms that support dy*namic multithreading*, such as dialects of Cilk [56, 106, 146, 196, 237, 246], Fortress [11], Habanero [33], Habanero-Java [82], Hood [59], HotSLAW [283], Java Fork/Join Framework [233], OpenMP [26, 305], Task Parallel Library [245], Threading Building Blocks (TBB) [330] and X10 [87], have been developed that relieve programmers of the need to explicitly deal with concurrency or load-balance a parallel program. Dynamic multithreading concurrency platforms typically support the programming model of *fork-join parallelism*, in which subroutines can be spawned in parallel with little overhead. With dynamic multithreading, spawning a subroutine allows, but does not require, that subroutine to execute in parallel. The spawning of subroutines generates a series-parallel execution dag (directed acyclic graph) in which the synchronization of subtasks is managed "under the covers" by the runtime system. Constructs such as parallel loops can be implemented as syntactic sugar on top of the fork-join model. Dynamic multithreading concurrency platforms usually schedule the computation using randomized work-stealing [24, 56, 58, 146], where worker threads in the runtime system coordinate to load-balance the computation. Hence, dynamic multithreading provides a *processor-oblivious* model of parallel computation, in which programmers only expose logical parallelism without referring to the physical processor cores on the machine. Dynamic multithreading has grown in popularity to the point that mainstream compilers, such as GCC [369], ICC [198], and LLVM [232], now support the dynamic multithreading linguistics provided by Cilk Plus [151, 195] and OpenMP [152, 262].

Dynamic multithreading supports a principled approach to reasoning about parallel program correctness and scalability. Intuitively, as long as a parallel program contains no *determinacy races* [134] (also called *general races* [297]), then the program is deterministic, and it therefore exhibits serial semantics. Moreover, efficient tools exist that can guarantee to detect determinacy races or validate their absence [119, 134, 135, 324, 325, 392]. The fork-join model also supports theoretical analysis of program performance and scalability in terms of the program's "work" and "span" [100, Ch. 27], and concurrency platforms can ensure that the performance predictions from work-span analysis are often borne out in practice [146, 180]. Efficient tools exist for analyzing a program's scalability based work-span analysis [180].

Despite this progress, however, these technologies remain immature, and their shortcomings still leave programmers to deal with complex nondeterminism and scalability issues. How, for example, do dynamic multithreading platforms support efficient parallel computations on irregular structures (i.e., graphs), computations that use pseudorandom numbers, or computations that exhibit pipeline parallelism that emerges dynamically? How can programmers quickly see how different parts of a dynamic multithreaded program contribute to its "work" and "span?" How can programmers detect determinacy races in programs that use advanced programming features? How can compilers support performance engineering of dynamic multithreaded codes? The artifacts presented in this thesis shed light on these questions.

# 1.2 Developing simple programming models and theories of performance

The first five artifacts presented in this thesis (Chapters 3 through 7) explore the development of two key technologies to support a science of fast code: simple programming models and theories of performance that are borne out in practice. This section describes these two technologies as well as the five artifacts in this thesis that explore their development.

Simple programming models, such as the fork-join model of dynamic multithreading, can support principled approaches to reasoning about program behavior. Efficient multicore software, for example, must deal effectively with complex issues such as atomicity, nondeterminism, scheduling, and load-balancing. Programming models can simplify fast code by encapsulating "ugly" aspects of computer hardware and providing programmer-friendly abstract properties such as processor obliviousness, determinism, serial semantics, and composable performance. An analogy can be made with **goto** statements and the structured control-flow statements — e.g., conditionals and loops — that replaced them in modern serial programming languages. Similarly to how structured control-flow statements facilitates reasoning about the serial program behavior, simple programming models can make multicore programs easier to reason about than their traditional Pthreaded counterparts.

Some programming models support the powerful feature that they admit theories of performance that are borne out in practice, which support principled approaches to reasoning about software efficiency. Consider the randomized work-stealing schedulers [24, 56, 58, 146] employed by dynamic multithreading concurrency platforms. These schedulers offer theoretical guarantees on how efficiently they execute a parallel program. By using these schedulers, programmers can predict how a parallel program will scale on any number of processors without having to write an optimized implementation and test it on a variety of machines and core counts. Moreover, programmers can perform back-of-the-envelope calculations based on work-span analysis to check whether parallel software meets its theoretical performance expectations or fails to do so due to a programming bug or an unanticipated factor that inhibits scalability. Because these theories of performance are borne out in practice, programmers can use the

The artifacts presented in this section address a variety of parallel programming challenges using dynamic multithreading, specifically, Cilk technology [56,106,146,196,237,246]. Cilk supports a fork-join model of parallelism and employs a randomized work-stealing scheduler that schedules and load-balances programs efficiently, both in theory and in practice [146]. Modern dialects of Cilk [196,237,246] also support "reducer hyperobjects" [144], an advanced programming feature for managing concurrent accesses to shared variables.

The five artifacts overviewed in this section — "PBFS," "Prism," "Color," "DPRNG," and "Cilk-P" — explore how Cilk's programming model and theoretical performance guarantees can be employed and enhanced to support a wider variety of parallel computations. The "PBFS," "Prism," and "Color" artifacts examine how to parallelize algorithms on graphs to provide provable guarantees on efficiency that are borne out in practice. Graph computations are generally challenging to perform efficiently in parallel, because the irregular structure of a graph complicates the scheduling and load-balancing of these computations on parallel cores. The "DPRNG" artifact tackles the problem of generating pseudorandom numbers deterministically in parallel in dynamic multithreaded codes. The "Cilk-P" artifact studies the problem of writing and efficiently scheduling programs that exhibit both fork-join parallelism and pipeline parallelism that arises dynamically "on-the-fly."

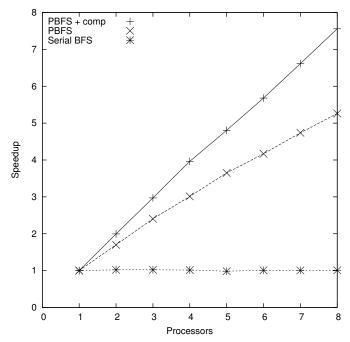

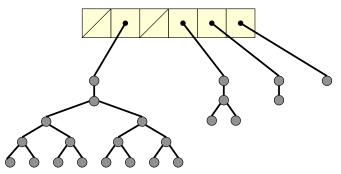

#### PBFS

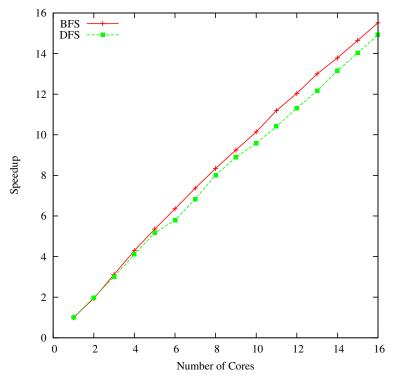

Chapter 3 presents PBFS [248], a "work-efficient" parallel breadth-first search (BFS) algorithm, which exhibits high work efficiency and achieves parallel speedup in both theory and practice.<sup>7</sup> In the standard serial BFS algorithm, the FIFO queue imposes a serial bottle-neck that is difficult to parallelize effectively. PBFS replaces this queue with an efficient implementation of a multiset data structure, called a "bag," which allows PBFS to achieve parallel speedup in practice. On a variety of benchmark input graphs, PBFS runs as fast on a single processor as a tight implementation of the standard serial BFS algorithm, and it speeds up linearly with processors.

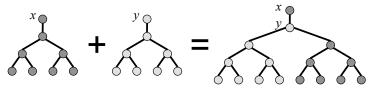

PBFS offers theoretical guarantees that support its performance in practice. PBFS is implemented in Cilk and employs Cilk's "reducer hyperobject" mechanism [144] to efficiently coordinate concurrent updates to bags. Because the Cilk runtime system maintains reducers based on how it schedules and load balances the computation, the work inherent in a PBFS execution is nondeterministic. My coauthor and I enhanced the dag model of Cilk dynamic multithreading to build a general theoretical performance model for analyzing Cilk programs that use reducers. Analyzing PBFS in this model shows that PBFS is **work***efficient*, meaning that it performs asymptotically the same number of operations as its serial counterpart, the standard serial BFS algorithm. Furthermore, this analysis shows that PBFS achieves linear speedup on as many processors as the size of the graph divided by its diameter, up to polylogarithmic factors.

PBFS's theoretical guarantees offer assurance that the PBFS algorithm scales well when applied to other parallel software. Intel used PBFS to implement a parallel version of the

<sup>&</sup>lt;sup>7</sup>I collaborated with Charles E. Leiserson on this work.

Murphi model checker [118] that achieves near-perfect parallel speedup, specifically, a 15.5 factor speedup on 16 cores.

#### Prism

Chapter 4 presents the PRISM and PRISM-R "chromatic-scheduling" algorithms for executing "dynamic data-graph computations" efficiently and deterministically in parallel [213].<sup>8</sup> A data-graph computation consist of rounds of updates, where each update recomputes the value associated with a vertex in a graph. A dynamic data-graph computation updates only a subset of the graph's vertices in each round. When executing a data-graph computation in parallel, locks are often employed to ensure that updates are performed atomically. Locks not only incur overhead, but they also cause updates to occur in a nondeterministic relative order.

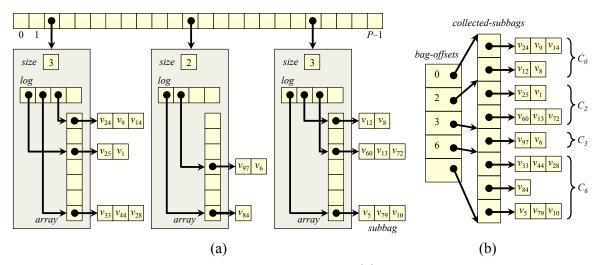

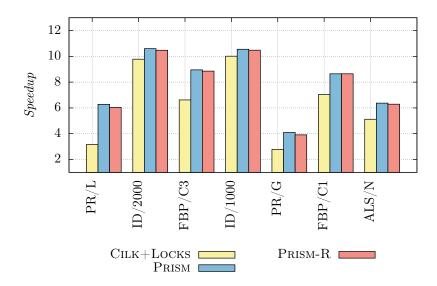

Instead of locks, PRISM uses "chromatic scheduling" [2, 43, 264] to coordinate parallel updates in a dynamic data-graph computation. Conceptually, PRISM precomputes a vertexcoloring of the graph of dependencies between updates, and then executes each round of the data-graph computation based on the coloring: vertices of different colors are updated in a fixed order, while vertices of the same color are updated in parallel. PRISM thereby ensures that the dynamic data-graph computation executes deterministically, allowing programmers to reason about the program's correctness based on its serial semantics. PRISM employs an efficient implementation of a novel "multibag" data structure to maintain dynamic sets of vertices partitioned by color. PRISM provides theoretical guarantees on its scalability, based on the size of the graph, the size of each round, and the number of colors used in the vertex-coloring. In practice, by avoiding the overheads of locking, PRISM executes dynamic data-graph computations faster than lock-based alternatives, despite imposing the restrictive requirement of deterministic execution. By providing theoretical guarantees that are borne out in practice, programmers can rely on PRISM to execute dynamic data-graph computations efficiently.

An extension of PRISM, called PRISM-R, handles dynamic data-graph computations whose updates perform associative operations on global variables. PRISM-R employs an efficient implementation of a novel "multivector" data structure, in place of PRISM's "multibag," to efficiently maintain ordered sets of vertices partitioned by color. PRISM-R provides the same theoretical guarantees on its scalability to those of PRISM, and runs nearly as quickly as PRISM in practice.

#### Color

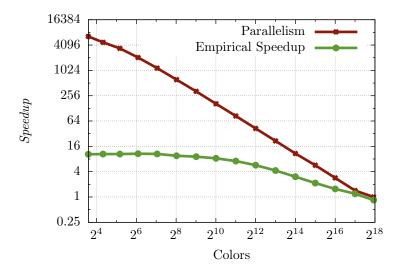

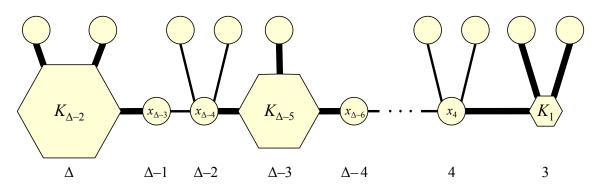

Chapter 5 presents the "largest-log-degree-first" (LLF) and "smallest-log-degree-last" (SLL) ordering heuristics for greedy graph-coloring algorithms [175].<sup>9</sup> These ordering heuristics seek to eliminate a tradeoff between coloring quality and parallel performance. Greedy graph-coloring algorithms often use ordering heuristics, such as "largest-degree-first" and "smallest-degree-last," to reduce the number of colors they use in practice. My coauthors and I show, however, that there exist input graphs on which these heuristics can create serial bottlenecks when applied to parallel graph-coloring algorithms. The LLF and SLL ordering heuristics aim to get the best of both worlds. Not only do these heuristics color graphs using

<sup>&</sup>lt;sup>8</sup>PRISM and PRISM-R were developed in collaboration with Tim Kaler, William Hasenplaugh, and Charles E. Leiserson.

<sup>&</sup>lt;sup>9</sup>I collaborated with William Hasenplaugh, Tim Kaler, and Charles E. Leiserson on this work.

a comparable number of colors to the analogous largest-degree-first and smallest-degree-last heuristics, but unlike their serial analogs, LLF and SLL provide theoretical guarantees on parallel scalability and achieve parallel speedup in practice. Programmers can therefore employ these heuristics in graph-coloring codes with confidence that they will not inhibit scalability, and they can use the theoretical guarantees to understand the performance of these graph coloring codes quantitatively.

#### DPRNG

Chapter 6 introduces the DOTMIX library and the "pedigree" mechanism to support deterministic parallel random-number generation in dynamic multithreaded programs [249].<sup>10</sup> To debug a serial program that uses pseudorandom numbers, programmers can fix the seed of the random-number generator to make it behave deterministically. Standard approaches to parallel random-number generation, however, produce pseudorandom numbers nondeterministically in dynamic multithreaded programs, even when the programmer uses a fixed seed. These approaches involve either synchronizing concurrent accesses to a common randomnumber generator or using separate random-number generators per processor. With either approach, the nondeterminism of parallel scheduling can change the pseudorandom numbers generated. Although some solutions to deterministic parallel random-number generation exist for Pthreaded programs [92,273,338], these solutions either do not scale or do not directly apply to dynamic multithreaded programs.

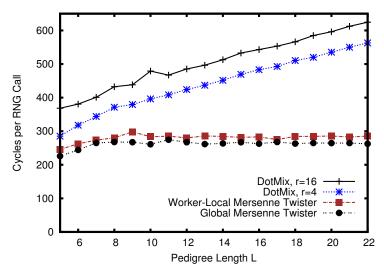

DOTMIX generates pseudorandom numbers in parallel, such that its behavior is deterministic for a fixed seed. The DOTMIX library thus simplifies the programming model for randomized dynamic multithreaded programs by providing linguistics to support serial semantics and repeatable execution. DOTMIX generates pseudorandom values of comparable statistical quality to the popular Mersenne twister random-number generator [274] while incurring little overhead — less than 21% on realistic benchmarks — compared to using Mersenne twister nondeterministically. These properties ensure that programs that use DOTMIX still use high-quality pseudorandom numbers and pay minimal performance to enjoy deterministic behavior.

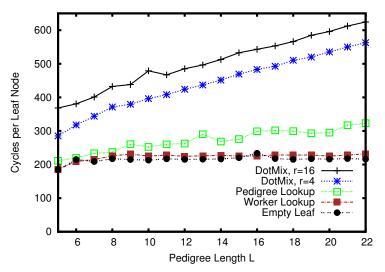

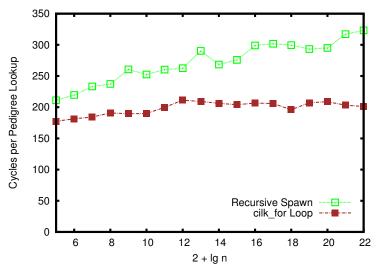

DOTMIX requires support from the runtime system and compiler to generate pseudorandom numbers deterministically. DOTMIX in particular uses our "pedigree" mechanism, which assigns a unique ID to each program point in a dynamic multithreaded program in a schedule-independent manner. To generate a pseudorandom number, each call to the rand routine in the DOTMIX library extracts the pedigree of the current program point and hashes it using a provably good hash function. This hash function guarantees a low probability that two ID's hash to the same value; formally, this hash function is 2-independent. Pedigrees incur negligible overhead in a runtime system, specifically, less than 1% overhead in the MIT Cilk runtime system.

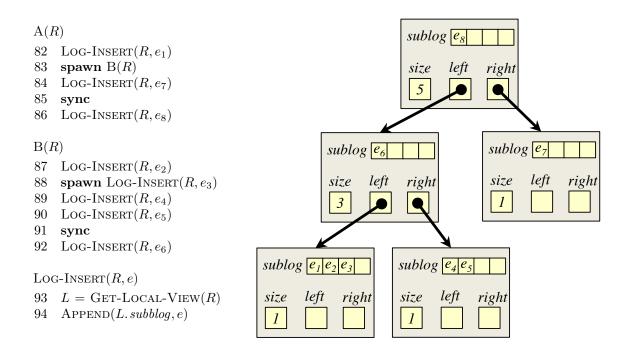

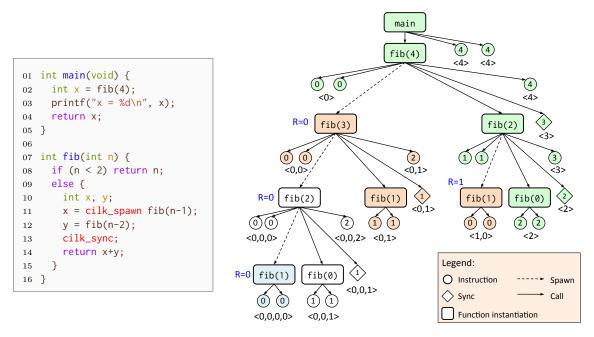

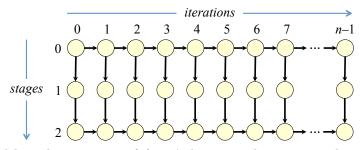

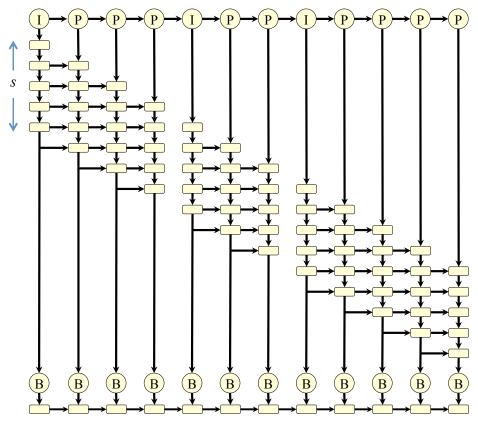

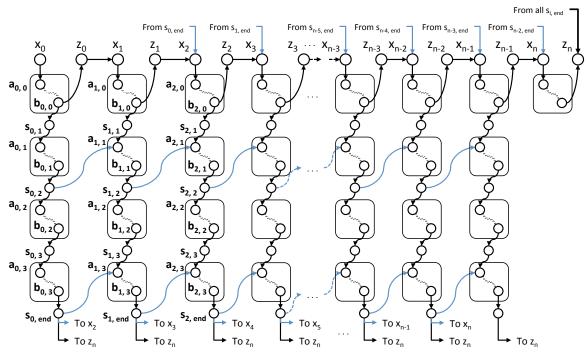

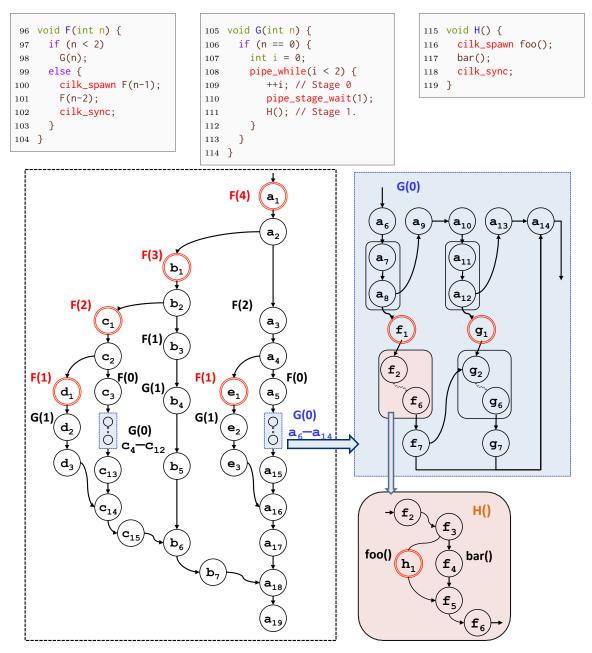

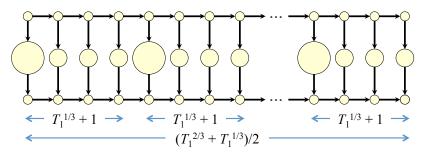

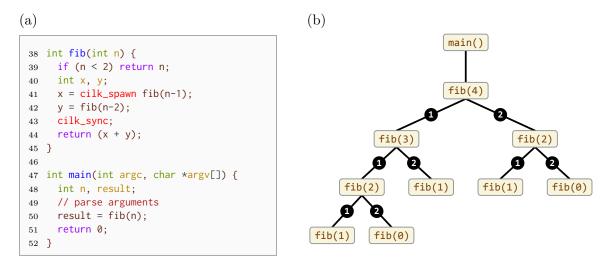

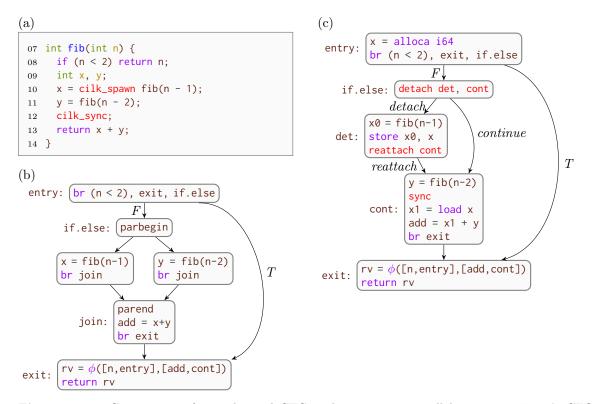

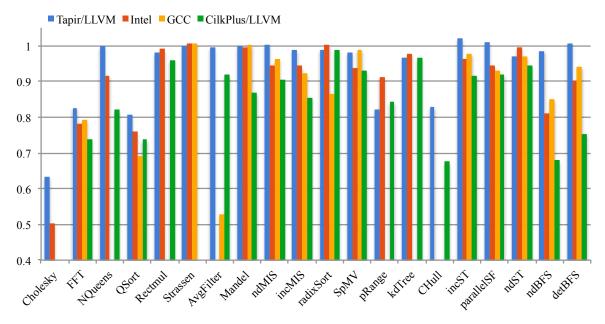

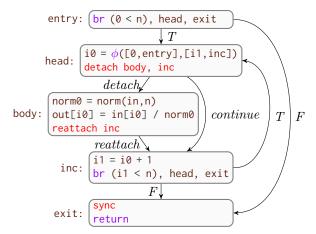

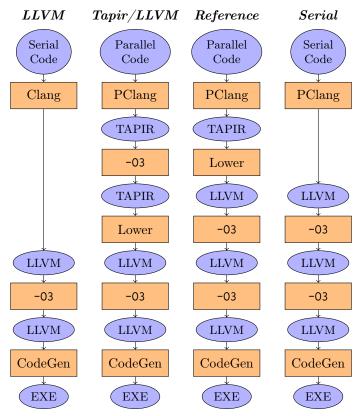

#### Cilk-P